## High-performance Scalable Photonics On-chip Network for Many-core Systems-on-Chip

## Achraf Ben Ahmed

A DISSERTATION SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE AND ENGINEERING

Adaptive Systems Laboratory Graduate Department of Computer and Information Systems University of Aizu, Japan

March 2016

The thesis titled

### High-performance Scalable Nanophotonics On-chip Network for Many-core Systems

by

### Achraf Ben Ahmed

is reviewed and approved by:

| Chief referee              |          |         |       |

|----------------------------|----------|---------|-------|

| Professor                  | $\sum$   | 110     |       |

| Abderazek Ben Abdallah     | 15en     | Alder   | borth |

| Professor                  | 1        | 0 \     | AS    |

| Toshiyaki Miyazaki         | 7.my     | arake   |       |

| Professor                  | 1        | 0 1     | (重)   |

| Tsuneo Tsukahara           | U. J.S.  | Kichera | (策)   |

| Professor                  |          |         | B     |

| Anh T. Pham                | Anh T.   | PHAM    | 3     |

| Senior Associate Professor | 1        | , /     |       |

| Yukihide Kohira            | Mukihide | Kohina  | (二)   |

|                            | 1        | 100     |       |

University of Aizu

March 2016

Dedicated to

my lovely Mother,

my Father, and to the rest of my Family

### High-performance Scalable Nanophotonics On-chip Network for Many-core Systems

Achraf Ben Ahmed

Submitted for the Degree of Doctor of Philosophy March 2016

#### Abstract

The continuous increasing demand for higher performance computing systems and aggressive technology scaling has driven the trend of integrating large number of cores in a single chip. In future generations of high-performance many-core systems, the efficiency of the communication infrastructure is as important as the computation efficiency of individual cores. Conventional electrical Networks-on-Chip (NoCs) are expected to reach their limits with increasing core counts because of high power dissipation and reduced performance.

As indicated in the latest version of ITRS roadmap, photonic wiring is a promising interconnect paradigm for future system-on-chip (SoC) designs that can provide broadband data transfer rates unmatchable by the existing metal interconnects. When combined with Wavelength Division Multiplexing (WDM), multiple parallel optical streams of data are concurrently transferred through a single waveguide. This contrasts with the Electronic Networks-on-Chip (ENoCs) that require a unique metal wire per bit stream. The key to saving power in on-chip photonic communication comes from the fact that once a photonic path is established, the optical data is transmitted in an end-to-end fashion without the need for buffering, repeating, or regenerating.

The photonic switching/routing techniques, configuration and routing algorithm directly affect the performance and power characteristics of future many-core on-chip Photonic communication. In particular, the control module and the path configuration algorithm, which orchestrate the different electrical control function play a In this dissertation, a set of novel photonic routing algorithms and architectures are proposed for future on-chip optical networks.

First, a new low-latency, non-blocking photonic switch/router (NBPS) and its control module capable of handling all photonic communication configuration tasks is proposed. The proposed approach is based on a new hybrid spatial switching mechanism for the photonic data stream transfer and is done by manipulating the state of the broadband switching elements. In addition, the NBPS is based on a Wavelength-Selective-Switching (WSS) for handling all communication configuration tasks.

Second, a new contention-aware path configuration algorithm and architecture for Electro-Assisted Photonic Network-on-Chip (EA-PNoC) is proposed. In addition to the main configuration tasks, the algorithm also decouples the Electronic Control Network (ECN) from the Photonic Communication Network (PCN) in a manner that both photonic and electric domains work independently from each other. The proposed algorithm orchestrates the different path configuration packets processes and significantly alleviates the contention in the ECN.

Third, a low-complexity routing and configuration algorithm for EA-PNoC is proposed. The approach is mainly based on photonic components augmented with a simple electronic control module and a so-called wavelength-shifting mechanism. The main merit of this new approach is to configure the path using photonic devices instead of the typical power-hungry electronic router.

The proposed architectures and algorithms were evaluated with a discrete-event simulator, which incorporates detailed physical models of the photonic components. Results show that we could achieve better energy efficiency, as well as a considerable reduction in the blocking occurrence, which is the main source of latency and bandwidth degradation in conventional EA-PNoCs.

### オンチップメニーコアシステムのための高性能、高拡 張性フォトニクスオンチップネットワーク

#### ベン アメド アシュラフ

### 博士号学位のために 2016 年 3 月に提出

### 概要

高性能計算システムやより高度な微細化技術への需要の高まりは、単一チップ上に より多くのコアを統合するという手法へと向かわせた。次世代の高性能計算用メニ ーコアシステムにおいて、効率的な通信基盤は、単独のコアの計算効率と同様に重 要である。現在 electrical Networks-on-chips (NoCS) は、コア数の増加にとも なう電源不足や性能低下の問題へアプローチする手法として期待されている。

ITRS ロードマップの最新版が示す通り、フォトニックワイアリングは、既存のメ タルによる相互配線と適合しない広帯域データ転送レートを提供する将来的な system-on-chip (SoC) 設計への有望なパラダイムである。Wavelength Division Multiplexing (WDM)と組み合わせたとき、複数の並列した光学データストリームは 単一の導波管 (waveguide) に同時に転送される。 これは Electronic Networkson-Chip (ENoCs) がビットストリームごとに別々のメタル配線を要することと、対 称的である。

光学スイッチング・ルーティング技術、配置手法、ルーティングアルゴリズムは、 将来的なメニーコアのオンチップ上光学通信の性能と消費電力の特性に直接影響す る。とりわけ、異なる電子制御機能を編成する、制御モジュールと経路設定アルゴ リズムは、電気的なリソースと光学的なリソース両方をどうやって利用するかとい う点で、重要な役割を担っている。本論文では、将来的なオンチップの光学ネット ワークのための、革新的な光学ルーティングアルゴリズムとアーキテクチャのセッ トを提案している。

第一に、新しい低レイテンシ non-blocking photonic switch/router (NBPS) と、 全光学通信の設定タスクを扱える制御モジュールを提案する。この提案手法は、光 学データストリーム転送のための新しいハイブリッド空間のスイッチング機構をベ ースとし、広帯域スイッチングエレメントの状態を操作することで行われる。くわ えて、この NBPS は、全ての通信設定タスクを扱う Wavelength-Selective-Switching (WSS)の上に成り立っている

第二に、新しい contention-aware 経路設定アルゴリズムとアーキテクチャを提案 する。メインの設定タスクに加えて、このアルゴリズムは、光学的領域と電気的領 域でそれぞれ個別に動作するシステムの、the Electronic Control Network (ECN) を Photonic Communication

Network (PCN)から分離させている。本提案手法は、ECN中の競合の処理をし著し く緩和する、異なるパスセットアップパケットを編成する。

第三に、ハイブリッド光学 Network-on-Chip のための低複雑性ルーティングおよび設定アルゴリズムを提案する。この手法は主に、シンプルな電気的制御モジュールといわゆる wavelength shifting 機構によって強化された光学デバイスをベースとしている。

## Declaration

The work in this thesis is based on research carried out at the Adaptive Systems Laboratory at the University of Aizu, Japan. No part of this thesis has been submitted elsewhere for any other degree or qualification and it is all my own work unless referenced to the contrary in the text.

#### Copyright © 2016 by Achraf Ben Ahmed.

"The copyright of this thesis rests with the author. No quotations from it should be published without the author's prior written consent and information derived from it should be acknowledged".

## Acknowledgements

I would like to express my sincere gratitude to my advisor Prof. Prof. Abderazek Ben Abdallah for the continuous support of my Ph.D study and research, for his patience, motivation, enthusiasm, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis.

I would like to thank also Prof. Toshiyaki Miyazai, Prof. Tsuneo Tsukahara, Prof. Anh Pham, and Prof. Yukihide Kohira of the University of Aizu for taking the time to revise my thesis. Moreover, my sincere gratitude to Prof. Yuichi Okuyama for his help and support during the past three years.

I would also like to thank my family for the support they provided me through my entire life and in particular, I must acknowledge my parents, without whose love, encouragement and editing assistance, I would not have finished this thesis.

Last but not least, I would like to thank all my friends back home and in Japan. Especially, the members of the Adaptive Systems Laboratory at the University of Aizu. They facilitated my integration in the Japanese society with their valuable advice, making my stay in Japan much easier and more comfortable.

## Contents

|          | Ab   | stract  |            |                                       | iv   |

|----------|------|---------|------------|---------------------------------------|------|

|          | Dec  | laratio | on         |                                       | viii |

|          | Ack  | nowle   | dgments    |                                       | ix   |

| 1        | Intr | oducti  | ion        |                                       | 1    |

|          | 1.1  | Curren  | nt System  | Design                                | . 1  |

|          | 1.2  | Electr  | onic Netw  | vork-on-Chip                          | . 4  |

|          | 1.3  | Photo   | nic Interc | onnect                                | . 6  |

|          | 1.4  | Photo   | nic Netwo  | orks-on-Chip: Problems and Motivation | . 8  |

|          | 1.5  | Thesis  | o Objectiv | es and Contributions                  | . 9  |

|          | 1.6  | Thesis  | outline    |                                       | . 10 |

| <b>2</b> | Bac  | kgrou   | nd: Phot   | onic Networks-on-Chip                 | 12   |

|          | 2.1  | Photo   | nic Comn   | nunication                            | . 12 |

|          |      | 2.1.1   | Photonie   | c NoC Building Blocks                 | . 13 |

|          |      |         | 2.1.1.1    | Laser                                 | . 14 |

|          |      |         | 2.1.1.2    | Coupler                               | . 14 |

|          |      |         | 2.1.1.3    | Waveguide                             | . 14 |

|          |      |         | 2.1.1.4    | Micro-Ring Resonator                  | . 15 |

|          |      |         | 2.1.1.5    | Modulator                             | . 16 |

|          |      |         | 2.1.1.6    | Photodetector                         | . 17 |

|          | 2.2  | Routin  | ng Scheme  | es in PNoCs                           | . 17 |

|          |      | 2.2.1   | Circuit S  | Switching                             | . 19 |

|   |                                  | 2.2.2                                                                                     | Wavelen                                                                                                                       | gth-Routed                                   | . 19                                                                                                |

|---|----------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------|

|   |                                  |                                                                                           | 2.2.2.1                                                                                                                       | Source-based Routing                         | . 21                                                                                                |

|   |                                  |                                                                                           | 2.2.2.2                                                                                                                       | Destination-based Routing                    | . 21                                                                                                |

|   |                                  |                                                                                           | 2.2.2.3                                                                                                                       | Multiple Write Single Read                   | . 21                                                                                                |

|   |                                  |                                                                                           | 2.2.2.4                                                                                                                       | Single Write Multiple Read                   | . 22                                                                                                |

|   |                                  |                                                                                           | 2.2.2.5                                                                                                                       | Fully Connected Crossbar                     | . 23                                                                                                |

|   | 2.3                              | Photo                                                                                     | nic NoC I                                                                                                                     | Metrics                                      | . 24                                                                                                |

|   |                                  | 2.3.1                                                                                     | Power B                                                                                                                       | Budget                                       | . 24                                                                                                |

|   |                                  | 2.3.2                                                                                     | Data Int                                                                                                                      | tegrity                                      | . 24                                                                                                |

|   | 2.4                              | Chapt                                                                                     | er Summ                                                                                                                       | ary                                          | . 26                                                                                                |

| 3 | Dol                              | ated V                                                                                    | Vonka                                                                                                                         |                                              | 27                                                                                                  |

| J | 3.1                              |                                                                                           |                                                                                                                               | Photonic NoCs                                |                                                                                                     |

|   | 3.1                              |                                                                                           |                                                                                                                               | ed Photonic NoCs                             |                                                                                                     |

|   | 3.2<br>3.3                       |                                                                                           | -                                                                                                                             | NoCs Architectures                           |                                                                                                     |

|   | 3.3                              |                                                                                           |                                                                                                                               |                                              |                                                                                                     |

|   | <b>0.4</b>                       | Unapt                                                                                     | er summa                                                                                                                      | ary                                          | . 52                                                                                                |

|   |                                  | _                                                                                         |                                                                                                                               |                                              |                                                                                                     |

| 4 | Nor                              |                                                                                           | ing, Lov                                                                                                                      | v Latency Electro-Assisted Photonic NoC Arch |                                                                                                     |

| 4 | Nor<br>tect                      | n-block                                                                                   | ing, Lov                                                                                                                      | v Latency Electro-Assisted Photonic NoC Arch |                                                                                                     |

| 4 |                                  | n-block<br>Jure                                                                           |                                                                                                                               | v Latency Electro-Assisted Photonic NoC Arch | i-<br>33                                                                                            |

| 4 | tect                             | n-block<br>cure<br>Introd                                                                 | uction .                                                                                                                      |                                              | i-<br><b>33</b><br>. 33                                                                             |

| 4 | <b>tect</b><br>4.1               | n-block<br>sure<br>Introd<br>Syster                                                       | uction .<br>n Archite                                                                                                         | · · · · · · · · · · · · · · · · · · ·        | <b>- 33</b><br>. 33<br>. 33                                                                         |

| 4 | <b>tect</b><br>4.1<br>4.2        | n-block<br>cure<br>Introd<br>Systen<br>Electr                                             | uction .<br>n Archite<br>o-optic R                                                                                            |                                              | <b>33</b><br>. 33<br>. 33<br>. 34                                                                   |

| 4 | tect<br>4.1<br>4.2<br>4.3        | n-block<br>cure<br>Introd<br>Systen<br>Electr                                             | uction .<br>n Archite<br>o-optic R<br>IIC Non-H                                                                               | cture                                        | <b>33</b><br>. 33<br>. 33<br>. 34<br>. 41                                                           |

| 4 | tect<br>4.1<br>4.2<br>4.3        | n-block<br>Sure<br>Introd<br>Syster<br>Electr<br>PHEN                                     | uction .<br>n Archite<br>o-optic R<br>IIC Non-H                                                                               | cture                                        | <b>33</b><br>. 33<br>. 33<br>. 34<br>. 41<br>. 41                                                   |

| 4 | tect<br>4.1<br>4.2<br>4.3        | n-block<br>Sure<br>Introd<br>Syster<br>Electr<br>PHEN                                     | uction .<br>n Archite<br>o-optic R<br>IIC Non-H<br>Building                                                                   | cture                                        | <b>33</b><br>33<br>33<br>33<br>34<br>41<br>41<br>41<br>41                                           |

| 4 | tect<br>4.1<br>4.2<br>4.3        | n-block<br>Sure<br>Introd<br>Syster<br>Electr<br>PHEN                                     | uction .<br>n Archite<br>o-optic R<br>IIC Non-H<br>Building<br>4.4.1.1<br>4.4.1.2                                             | cture                                        | <b>33</b><br>. 33<br>. 33<br>. 34<br>. 41<br>. 41<br>. 41<br>. 43                                   |

| 4 | tect<br>4.1<br>4.2<br>4.3        | h-block<br>Jure<br>Introd<br>Syster<br>Electr<br>PHEN<br>4.4.1                            | uction .<br>n Archite<br>o-optic R<br>IIC Non-H<br>Building<br>4.4.1.1<br>4.4.1.2<br>Micro-R                                  | cture                                        | <b>33</b><br>. 33<br>. 33<br>. 34<br>. 41<br>. 41<br>. 41<br>. 43<br>. 43                           |

| 4 | tect<br>4.1<br>4.2<br>4.3        | h-block<br>Jure<br>Introd<br>System<br>Electr<br>PHEN<br>4.4.1                            | uction .<br>n Archite<br>o-optic R<br>IC Non-F<br>Building<br>4.4.1.1<br>4.4.1.2<br>Micro-R<br>Teardow                        | cture                                        | <b>33</b><br>33<br>33<br>34<br>41<br>41<br>41<br>41<br>43<br>43<br>43<br>43                         |

| 4 | tect<br>4.1<br>4.2<br>4.3        | h-block<br>fure<br>Introd<br>System<br>Electr<br>PHEN<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4 | uction .<br>n Archite<br>o-optic R<br>IIC Non-H<br>Building<br>4.4.1.1<br>4.4.1.2<br>Micro-R<br>Teardow<br>Optical            | cture                                        | <b>33</b><br>33<br>33<br>34<br>41<br>41<br>41<br>41<br>43<br>43<br>43<br>43<br>45<br>46             |

| 4 | tect<br>4.1<br>4.2<br>4.3<br>4.4 | h-block<br>fure<br>Introd<br>System<br>Electr<br>PHEN<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4 | uction .<br>n Archite<br>o-optic R<br>IC Non-H<br>Building<br>4.4.1.1<br>4.4.1.2<br>Micro-R<br>Teardow<br>Optical<br>Weight E | cture                                        | <b>33</b><br>33<br>33<br>34<br>41<br>41<br>41<br>41<br>43<br>43<br>43<br>43<br>43<br>45<br>46<br>49 |

|          |     | 4.5.3   | Network   | Interface and Gateway Architecture                  | 53 |

|----------|-----|---------|-----------|-----------------------------------------------------|----|

|          |     | 4.5.4   | Dimensi   | on-Order-Routing (DOR-XY)                           | 54 |

|          |     | 4.5.5   | Arbiter   | Architecture                                        | 54 |

|          | 4.6 | Chapt   | er Summ   | ary                                                 | 56 |

| <b>5</b> | Cor | ntentio | n-Aware   | e Path Configuration Algorithm                      | 57 |

|          | 5.1 | Introd  | uction .  |                                                     | 57 |

|          | 5.2 | Conte   | ntion-awa | re Path Configuration Algorithm                     | 57 |

|          |     | 5.2.1   | Path Co   | onfiguration Phases                                 | 59 |

|          |     |         | 5.2.1.1   | Path Setup                                          | 59 |

|          |     |         | 5.2.1.2   | ACK                                                 | 61 |

|          |     |         | 5.2.1.3   | Payload Transmission                                | 61 |

|          |     |         | 5.2.1.4   | Teardown                                            | 62 |

|          |     | 5.2.2   | Advanta   | ages of the Proposed Path Configuration Algorithm . | 63 |

|          | 5.3 | Evalua  | ation     |                                                     | 64 |

|          |     | 5.3.1   | Methode   | ology and Assumptions                               | 64 |

|          |     |         | 5.3.1.1   | Benchmarks                                          | 65 |

|          |     | 5.3.2   | Complex   | xity                                                | 66 |

|          |     | 5.3.3   | Latency   | Evaluation Under Synthetic Workloads                | 68 |

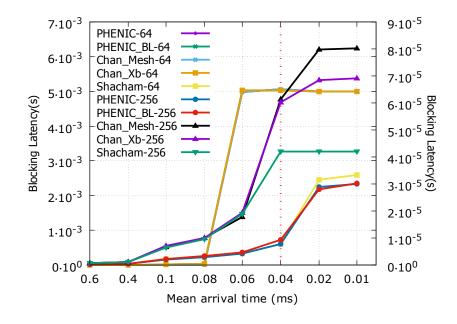

|          |     |         | 5.3.3.1   | Blocking Latency                                    | 68 |

|          |     |         | 5.3.3.2   | Blocked Requests                                    | 71 |

|          |     | 5.3.4   | Latency   | Evaluation Under Realistic Workloads                | 72 |

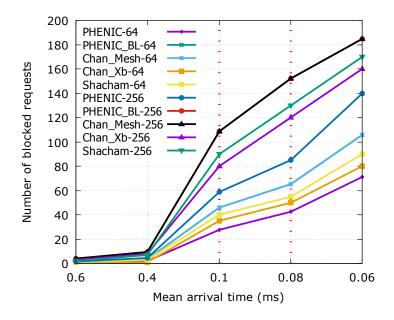

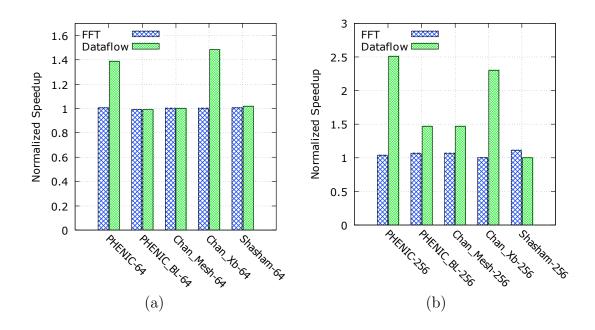

|          |     |         | 5.3.4.1   | Path Setup Latency Ratio                            | 72 |

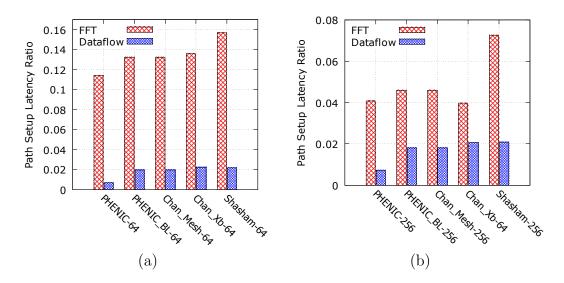

|          |     |         | 5.3.4.2   | Speedup                                             | 73 |

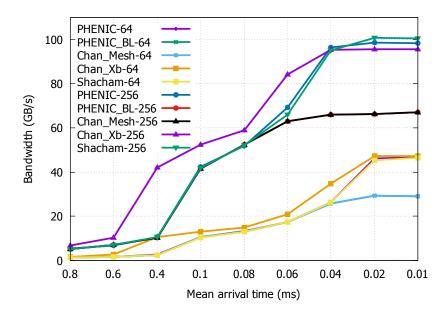

|          |     | 5.3.5   | Bandwid   | dth Evaluation Under Synthetic Workloads            | 74 |

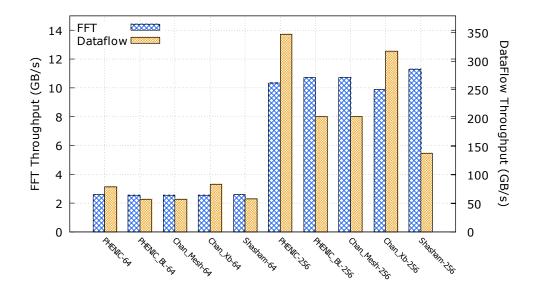

|          |     | 5.3.6   | Bandwie   | th Evaluation Under Realistic Workloads             | 75 |

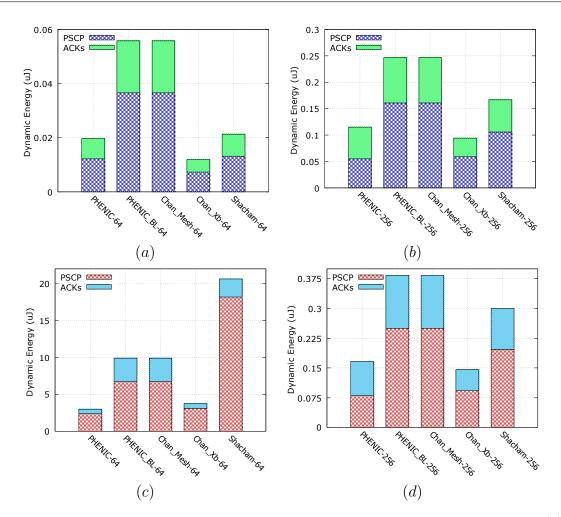

|          |     | 5.3.7   | Energy    | Evaluation Under Synthetic Workloads                | 75 |

|          |     |         | 5.3.7.1   | Path Configuration Energy Overhead                  | 75 |

|          |     |         | 5.3.7.2   | Total Power                                         | 78 |

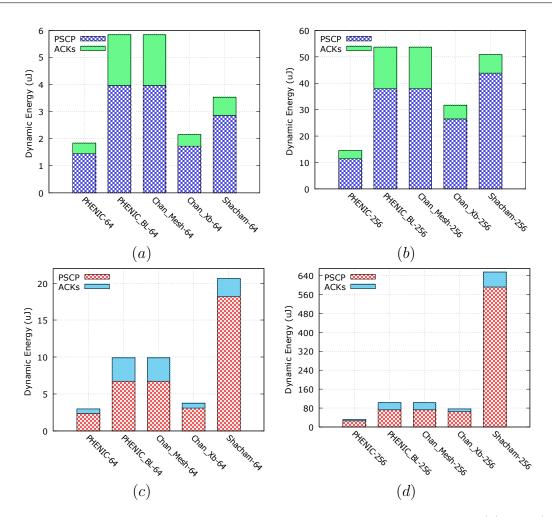

|          |     | 5.3.8   | Energy    | Evaluation Under Realistic Workloads                | 80 |

|          |     |         | 5.3.8.1   | Path Configuration Energy Overhead                  | 80 |

|          |     |         | 5.3.8.2   | Total Power                                         | 82 |

|   | 5.4             | Resul   | lts Summary                                           | 83  |

|---|-----------------|---------|-------------------------------------------------------|-----|

|   | 5.5             | Chapt   | er Summary                                            | 83  |

| 6 | Ene             | ergy-ef | ficient Wavelength-Shifting Routing Algorithm and Ar- |     |

|   | $\mathbf{chit}$ | ecture  |                                                       | 87  |

|   | 6.1             | Introd  | luction                                               | 87  |

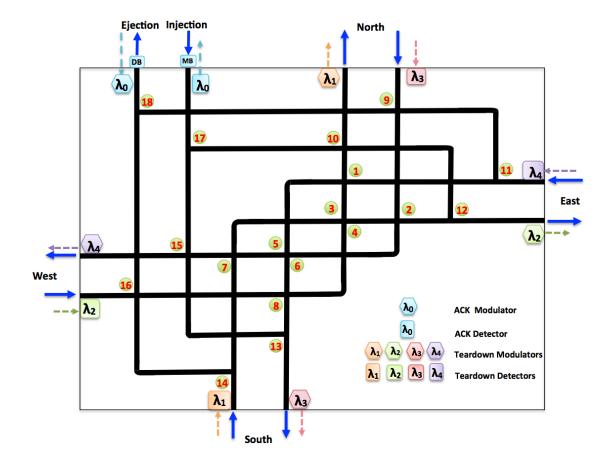

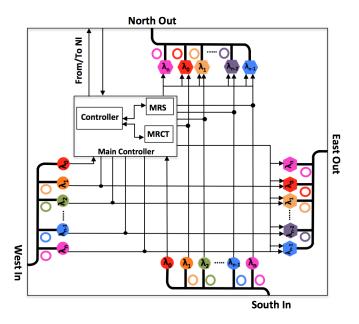

|   | 6.2             | Wavel   | ength-Routed Control Network Architecture             | 88  |

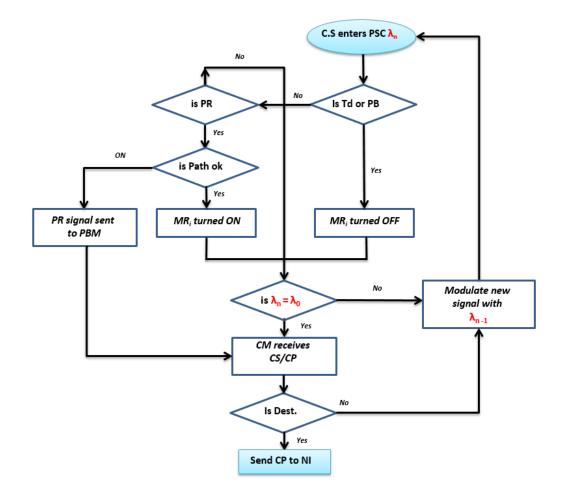

|   | 6.3             | Wavel   | ength-Shifting Routing Algorithm                      | 90  |

|   |                 | 6.3.1   | Routing Phases                                        | 90  |

|   |                 | 6.3.2   | Blocking Management                                   | 92  |

|   |                 | 6.3.3   | Case Study                                            | 93  |

|   | 6.4             | Evalua  | ation                                                 | 98  |

|   |                 | 6.4.1   | Methodology and Assumptions                           | 98  |

|   |                 | 6.4.2   | Complexity                                            | 98  |

|   |                 | 6.4.3   | Path Configuration Delay                              | 100 |

|   |                 |         | 6.4.3.1 Delay Under Light Traffic                     | 101 |

|   |                 |         | 6.4.3.2 Delay Under Heavy Traffic                     | 102 |

|   |                 | 6.4.4   | Mirco-Ring Release Time                               | 103 |

|   |                 | 6.4.5   | Bandwidth                                             | 104 |

|   |                 | 6.4.6   | Path Configuration Energy                             | 104 |

|   |                 |         | 6.4.6.1 Energy Under Light Traffic                    | 105 |

|   |                 |         | 6.4.6.2 Energy Under Heavy Traffic                    | 106 |

|   |                 | 6.4.7   | Energy Efficiency                                     | 107 |

|   |                 | 6.4.8   | Chapter Summary                                       | 108 |

| 7 | The             | esis Su | mmary and Discussion                                  | 109 |

|   | 7.1             | Contri  | ibutions Summary                                      | 109 |

|   | 7.2             | Resul   | lts Summary                                           | 110 |

|   | 7.3             | Discus  | ssion                                                 | 111 |

## List of Figures

| 1.1  | SOC design complexity trends                                             | 2  |

|------|--------------------------------------------------------------------------|----|

| 1.2  | Power consumption trends for communication-centric SoC design. $\ . \ .$ | 3  |

| 1.3  | Power consumption trends for computation-centric SoC design              | 4  |

| 1.4  | Network-on-Chip architecture                                             | 5  |

| 2.1  | Functional diagram of an optical communication.                          | 13 |

| 2.2  | Cross-section of a waveguide.                                            | 15 |

| 2.3  | Micrographs of a fabricated microring resonator                          | 16 |

| 2.4  | Micro-ring modulator                                                     | 16 |

| 2.5  | Circuit model of germanium detector with inductive gain peak             | 17 |

| 2.6  | Anatomy of EA-PNoC architecture.                                         | 18 |

| 2.7  | Anatomy of WR-PNoC architecture.                                         | 20 |

| 2.8  | Example of a source-based routing with four nodes                        | 21 |

| 2.9  | Example of a destination-based routing with four nodes                   | 22 |

| 2.10 | A Multi-Write Single-Read connection between four nodes                  | 22 |

| 2.11 | A Single-Read Multi-Write connection between four nodes                  | 23 |

| 2.12 | A fully connected crossbar connecting to four nodes                      | 23 |

| 2.13 | Different source of noise in a photonic link                             | 25 |

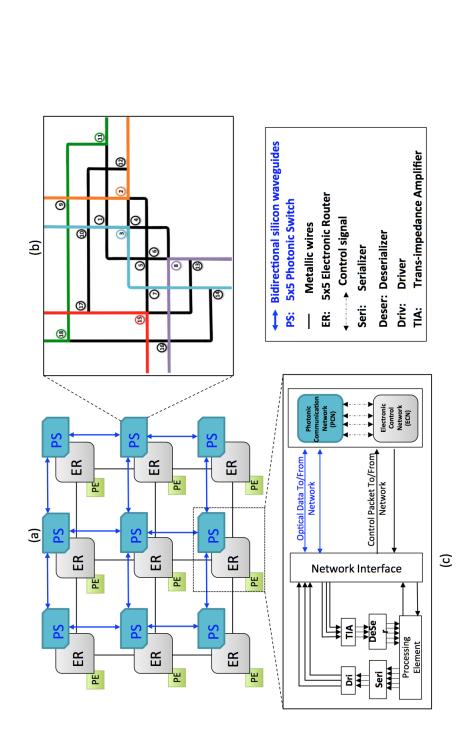

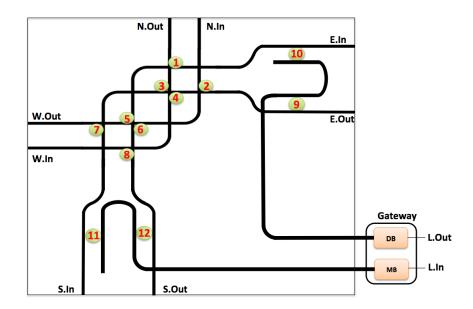

| 4.1  | PHENIC system architecture.                                              | 35 |

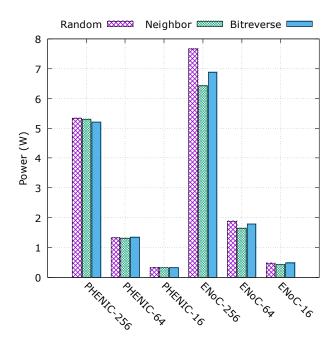

| 4.2  | Power consumption comparison results                                     | 36 |

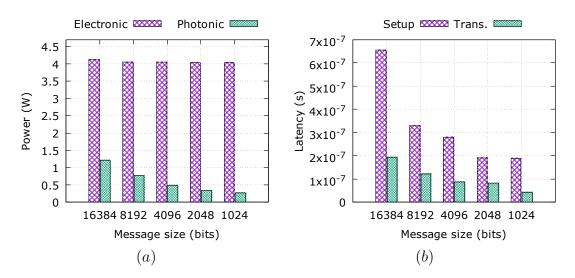

| 4.3  | PNoC's power and latency distributions.                                  | 37 |

| 4.4  | Input-buffer dynamic energy break-down before saturation                 | 38 |

| 4.5  | Example of 5x5 blocking switch                                           | 39 |

| 4.6  | Examples of dependency between the PSCP and Teardown packets             | 40 |

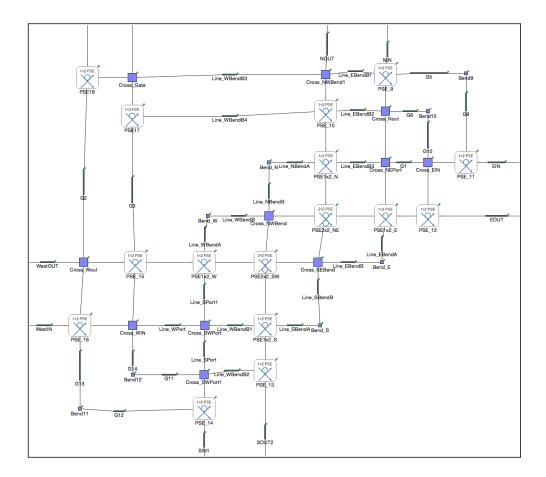

| 4.7  | PHENIC's non-blocking photonic switch                                   | 42 |

|------|-------------------------------------------------------------------------|----|

| 4.8  | Photonic siwtch building blocks                                         | 43 |

| 4.9  | Photonic switch building blocks instantiation.                          | 44 |

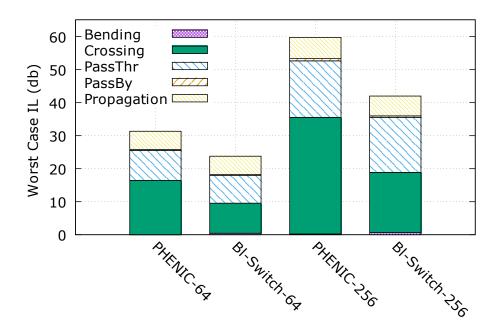

| 4.10 | Worst case optical power loss                                           | 48 |

| 4.11 | PHENIC's light-weight electronic router.                                | 50 |

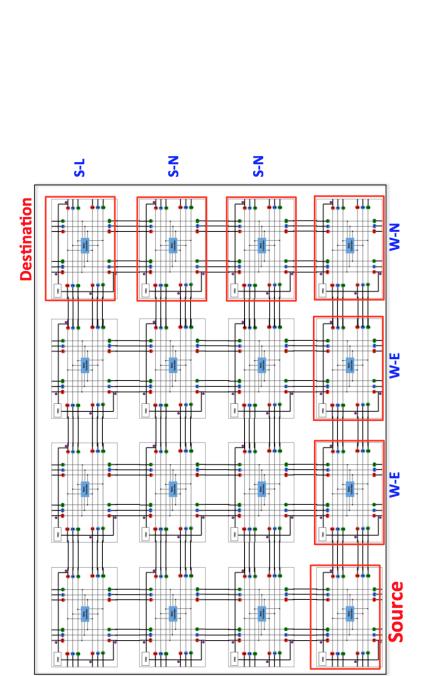

| 4.12 | Example of $4 \times 4$ interconnection network                         | 51 |

| 4.13 | PHENIC's electronic controller configuration packet size and format.    | 52 |

| 4.14 | PHENIC's gateway.                                                       | 53 |

| 4.15 | PHENIC's electronic and photonic arbiters.                              | 55 |

| 5.1  | Successful path-setup.                                                  | 59 |

| 5.2  | Failed path-setup                                                       | 60 |

| 5.3  | ACK phase                                                               | 61 |

| 5.4  | Payload transmission                                                    | 61 |

| 5.5  | Tear-down phase                                                         | 62 |

| 5.6  | Latency comparison results under random uniform traffic $\ . \ . \ .$ . | 70 |

| 5.7  | Average blocking latency comparison under random uniform traffic        | 71 |

| 5.8  | Number of blocked request comparison result                             | 72 |

| 5.9  | Average path setup ratio                                                | 73 |

| 5.10 | Normalized speedup comparison results                                   | 74 |

| 5.11 | Bandwidth comparison results under random uniform traffic               | 75 |

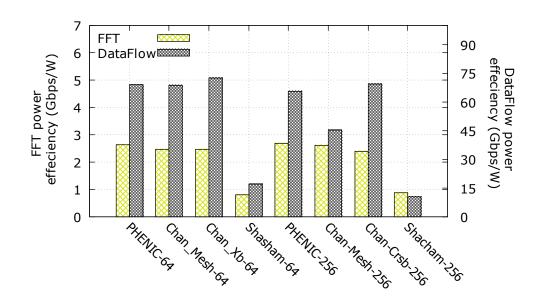

| 5.12 | Bandwidth comparison results under FFT and Dataflow workloads           | 76 |

| 5.13 | Path setup and acknowledgments energy for half-loaded network           | 77 |

| 5.14 | Path setup and acknowledgments energy near-saturation                   | 78 |

| 5.15 | Total energy and energy efficiency comparison results                   | 79 |

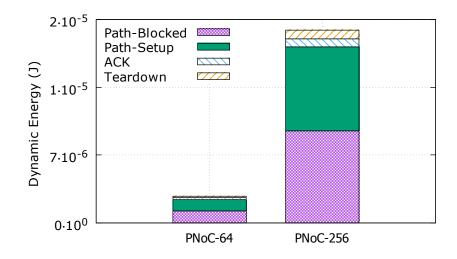

| 5.16 | Total Energy breakdown comparison                                       | 80 |

| 5.17 | Input-buffer dynamic energy breakdown near-saturation                   | 81 |

| 5.18 | Normalized path setup dynamic power per achieved bandwidth              | 81 |

| 5.19 | Power efficiency comparison results                                     | 82 |

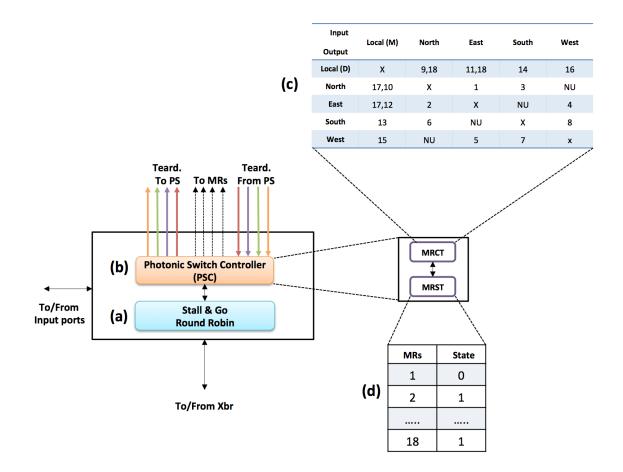

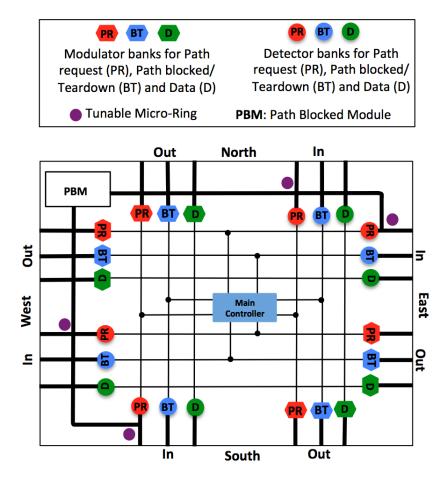

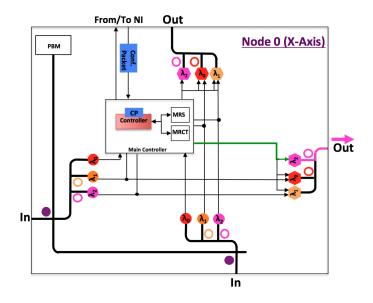

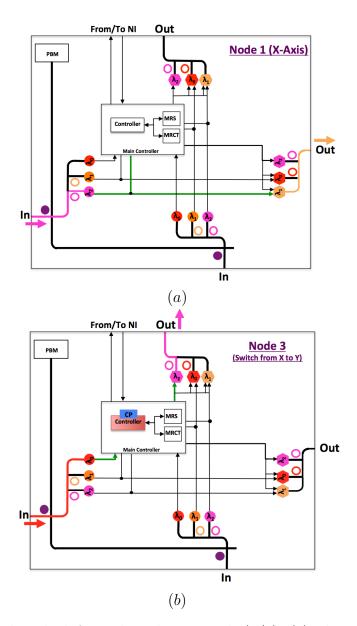

| 6.1  | Photonic switch controller                                              | 89 |

| 6.2  | Wavelength-shifting routing algorithm flowchart                         | 91 |

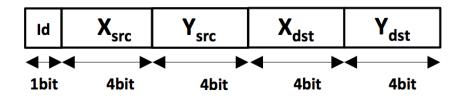

| 6.3  | Packet format generated at the sender network interface              | 91  |

|------|----------------------------------------------------------------------|-----|

| 6.4  | Micro architecture of the path request detector and modulator banks. | 92  |

| 6.5  | Micro architecture of the Path Blocked Manager.                      | 93  |

| 6.6  | Communication example in the wavelength-routed control network       | 94  |

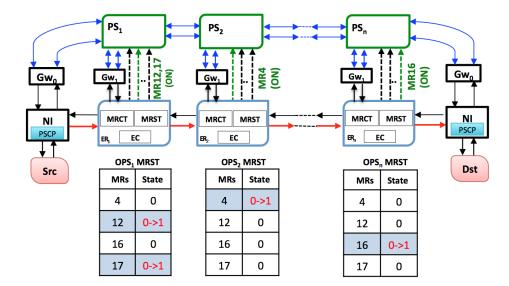

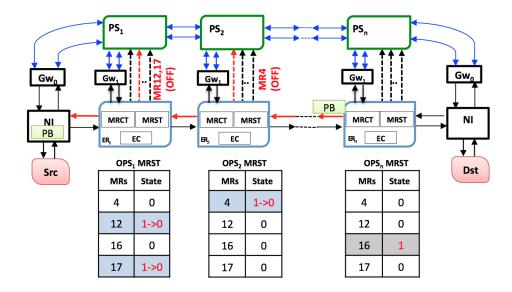

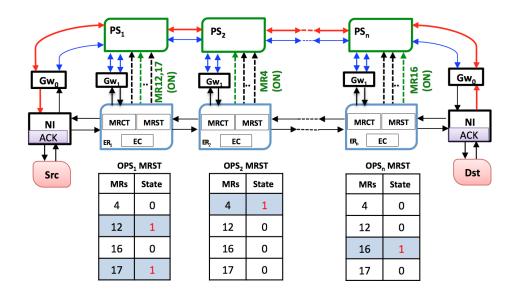

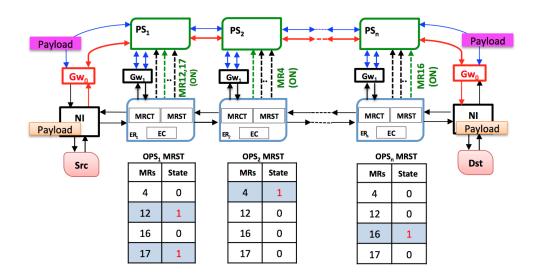

| 6.7  | Wavelength-shifting algorithm example $(1/3)$                        | 95  |

| 6.8  | Wavelength-shifting algorithm example $(2/3)$                        | 96  |

| 6.9  | Wavelength-shifting algorithm example $(3/3)$                        | 97  |

| 6.10 | Complexity and power comparison results                              | .00 |

| 6.11 | Path configuration delay under contention-less                       | .02 |

| 6.12 | Path configuration delay comparison results under contention 1       | .02 |

| 6.13 | Mirco-ring release time under contention-less                        | .04 |

| 6.14 | Offered bandwidth comparison results under contention-less 1         | .05 |

| 6.15 | Path configuration energy comparison results under contention-less 1 | .06 |

| 6.16 | Path configuration energy comparison results under contention 1      | .06 |

| 6.17 | Energy efficiency comparison results under contention-less 1         | .07 |

## List of Tables

| 4.1 | Micro-rings configuration for data transmission              |

|-----|--------------------------------------------------------------|

| 4.2 | Wavelength assignment for acknowledgment signals             |

| 4.3 | Insertion loss parameters                                    |

| 4.4 | Comparison between $5 \times 5$ optical routers              |

| 4.5 | Power loss comparison                                        |

| 5.1 | Configuration parameters                                     |

| 5.2 | Photonic communication network energy parameters             |

| 5.3 | Ring requirement comparison results for 64 cores systems 67  |

| 5.4 | Ring requirement comparison results for 256 cores systems 69 |

| 5.5 | Evaluation results summary under uniform random traffic 84   |

| 5.6 | Evaluation results summary under FFT workload                |

| 5.7 | Evaluation results summary under Dataflow workload           |

| 6.1 | Chip configuration                                           |

| 6.2 | Delay contribution for 32 nm technology nodes                |

| 6.3 | Energy contribution for 32nm technology nodes                |

## List of Abbreviation

| 3D-IC:   | Three dimensional Integrated Circuit                 |

|----------|------------------------------------------------------|

| 3D-NoC:  | Three dimensional Network-on-Chip                    |

| ACK:     | Acknowledgment                                       |

| BER:     | Bit Error Rate                                       |

| DB:      | Detector Bank                                        |

| DPE:     | Data Processing Element                              |

| DOR:     | Dimension Order Routing                              |

| DWDM:    | Dense Wavelength Division Multiplexing               |

| EA-PNoC: | Electro Assisted PNoC                                |

| E-NoC:   | Electronic Network-on-Chip                           |

| ECN:     | Electronic Control Network                           |

| EOR:     | Electro-Optic Router                                 |

| FCA:     | Free Carrier Absorption                              |

| ITRS:    | International Technology Road-map for Semiconductors |

| MB:      | Modulator Bank                                       |

| MRR:     | Micro-Ring Resonator                                 |

| MRCT:    | Micro-Ring Configuration Table                       |

| MRST:    | Micro-Ring State Table                               |

| MRRT:    | Micro-Ring Release Time                              |

| MPSoC:   | Multiprocessor Systems-on-Chip                       |

| MWSR:    | Multiple Write Single Read                           |

| NBPS:    | Non-Blocking Photonic Switch                         |

| NI:      | Network Interface                                    |

| P2P:     | Point-to-Point                                       |

| PBM:     | Path Blocked Module                        |

|----------|--------------------------------------------|

| PBP:     | Path Blocked Packet                        |

| PCD      | Path Configuration Delay                   |

| PCE      | Path Configuration Energy                  |

| PCN:     | Photonic Communication Network             |

| PE:      | Processing Element                         |

| PIC:     | Photonic Integrated Circuit                |

| P-NoC:   | Photonic Network-on-Chip                   |

| PR:      | Path Request                               |

| PSCP:    | Path Setup Control Packet                  |

| PSC:     | Photonic Switch Controller                 |

| SNR:     | Signal to Noise Ratio                      |

| SoC:     | System-on-Chip                             |

| SRMW:    | Single Write Multiple Read                 |

| TPA:     | Two Photon Absorption                      |

| TIA      | Trans-Impedance Amplifier                  |

| WDM:     | Wavelength Division Multiplexing           |

| WRCN:    | Wavelength-Routed Control Network          |

| WR-PNoC: | Wavelength-Routed Photonic Network-on-Chip |

| WSRA:    | Wavelength-Shifted Routing Algorithm       |

| WSS:     | Wavelenth Selective Switching              |

## Chapter 1

## Introduction

In this chapter, we give a background about the conducted research including the interconnect scalability issues in current System-on-Chips (SoCs) and how the Electronic Network-on-Chip (ENoC) is no longer scalable with the increase of the number of cores inside the chip. The Photonic Networks-on-Chip (PNoCs) are introduced as potential solutions to mitigate the E-NoCs problems. The routing algorithm is the main challenge when designing a PNoCs. Thus, the two approaches for routing optical data are introduced and discussed. We end this chapter with the main research objectives and contributions, as well as the outline of the thesis.

### 1.1 Current System Design

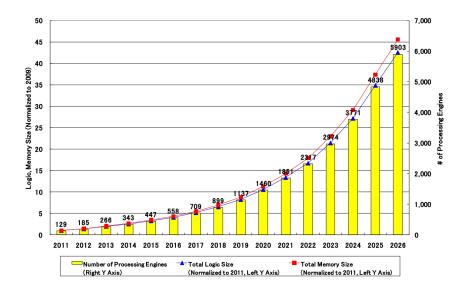

Over the past few decades, the advancement of computing systems is dominated by the rapid advances in semiconductor technology. This made possible the shrinking the chip size and the integration of hundred or even thousand of cores. Systems-on-Chip (SoCs) [1] are embedded systems composed of several modules on a single chip (processors, memories, input/output peripherals). With SoCs, it is now possible to process information and execute critical tasks at higher speed and lower power on a tiny chip. This is due to the increasing number of transistors that can be embedded on a single chip, which keeps doubling every 18 months as Gordon Moore predicted [2]. This made shrinking the chip size while maintaining high performance possible. This technology scaling has allowed SoCs to grow continuously in component count and complexity and evolve to systems with many processors embedded on a single die. As an example, the *Intel Xeon* processor [3] includes 2.3 billion transistors. With such high integration level, the development of many cores on a single die has become possible. These systems are called Multiprocessor Systems-on-Chip (MPSoC). For instance, the *Tilera Tile64* [4] and *Intel Polaris* [5] contain 64 and 80 cores, respectively. Figure 1.1 illustrates the SoC design com-

Figure 1.1: SOC design complexity trends [6].

plexity trends made by International Technology Roadmap for Semiconductors 2011 (ITRS) [6]. ITRS predicts that the number of Processing Elements (PEs) will grow rapidly in subsequent years to reach the 6000 PEs by 2026. Also, the amount of main memory is assumed to increase proportionally with the number of PEs. In the same way, the number of Data Processing Engines (DPEs) will increase significantly, leading to more than 70 TFlops processing performance [6].

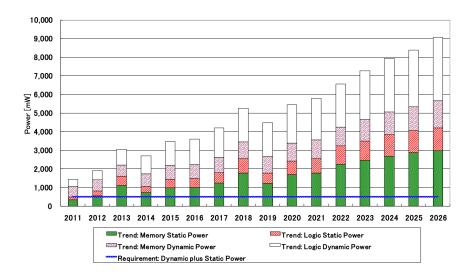

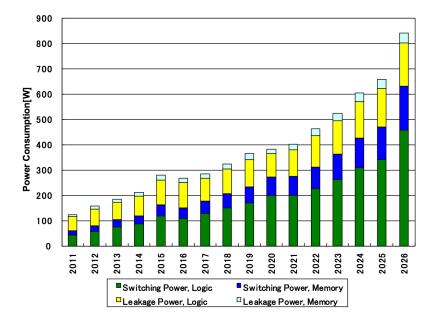

As the number of cores keeps increasing, and to efficiently take advantage of this large number, specific constraints must be taken into consideration. For example, design complexity, low energy dissipation, small silicon area, manufacturer and yield, resource management, etc.. In particular, the interconnection network starts to play a more and more important role in determining the performance and also the power consumption of the entire chip [7]. Interconnects consume more than 50% of dynamic power, and this percentage is expected to increase [8]. As a result of this significant increase in the number of PEs and DPEs, the power consumption will increase proportionally making the power consumption a key factor for the design of communication-concentric SoC. Even for performance-centric design, the power consumption remains a problem. Although the power consumption per DPE will decrease, this will be outweighed by the increase in the number of DPEs per chip, which results in critical chip packaging and cooling issues. This growth power demand is illustrated in Figs. 1.2 and 1.3. In addition to the growing of the

Figure 1.2: Power consumption trends for communication-centric SoC design [6].

number of PEs and DPEs inside the chip, this power consumption increase can be explained by the communication schemes used in such systems. The communication bottleneck can be driven by the fact that exploiting parallelism becomes a necessity and a must in the new architecture design to meet the performance requirement and the power constraints. However, parallelism implies an additional communication overhead due to the sharing and synchronization issues between threads and cores. Another aspect of the communication bottleneck is the I/O scaling frequency. While dramatic increases in on-chip frequencies have yielded huge performance gains over the last decades, this has not been the case for DRAM and other I/O what is usually referred to the memory wall [9].

Figure 1.3: Power consumption trends for computation -centric SoC design [6].

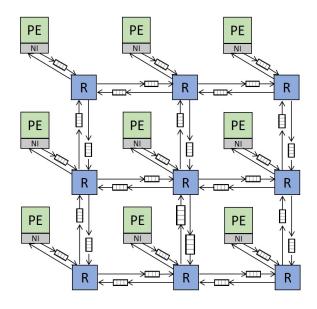

### 1.2 Electronic Network-on-Chip

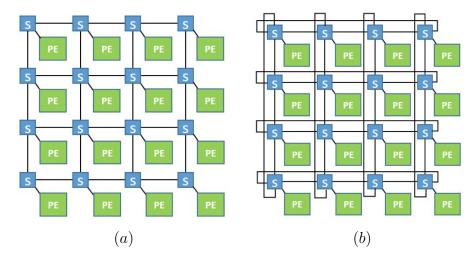

ENoCs (Electronic Network-on-Chip) [10-17] were introduced as a promising solution which can respond to the issues mentioned above. Based on a simple and scalable architecture platform, NoC connects processors, memory, and other custom designs together using switching packets on a hop-by-hop basis to provide a higher bandwidth and more enhanced performance. As shown in Fig.1.4, NoC architectures are based upon connecting segment (or wires) and switching blocks to combine the benefits of the previously proposed Point-to-Point (P2P) and sharedbus architectures, while solving their disadvantages, such as the large numbers of long wires in P2P and the lack of scalability in shared bus systems.

However, E-NoC represents serious scalability problems as the number of cores increases into hundred or thousand. This scalability problem concerns the three main metrics that affect the performance of an interconnection network which are throughput, latency, and power. As an example, in 2D mesh-based architecture, the channels, buffers, and crossbar are responsible for 15-30% of the total network power consumption [5].

This limitation comes basically from the high diameter that NoC suffers from.

Figure 1.4: Network-on-Chip architecture [10].

The network's diameter is the number of hops that a flit traverses in the longest possible minimal path between a pair of source and destination. The diameter is important for the NoC design since a large network diameter has an impact on the worst case routing latency in the network. For all these facts, the seek for optimizing NoC-based architecture becomes more and more necessary, and There has been much conducted research to achieve this goal through various approaches, such as developing fast routers [18–21] or designing new network topologies [22–24]. One of these proposed solutions was merging the Network-on-Chip to the third dimension (3D-NoC).

In fact, three-dimensional integrated circuits (3D-ICs) [25] have attracted much attention as a potential solution to resolve the interconnect bottleneck. A threedimensional chip is a stack of multiple device layers with direct vertical interconnects tunneling through them [26–29]. Research made so far have shown that 3D-ICs can achieve higher packing density due to the addition of a third dimension to the conventional two-dimensional layout. The average interconnects length can also be reduced as demonstrated in [30, 31], where a stochastic model for the global netlength distribution of a 3D-SoC is derived. In comparison to a 2D-SoC, the results prove that the use of three-dimensional architectures potentially reduces net length as the square root of the number of strata. This reduction in net length could lead to significant reductions in chip footprint area, power dissipation, and cycle time [32, 33], not forget to mention that circuitry is more immune to noise with 3D-ICs [25].

Feero et al. [15] showed that 3D-NoC has the ability to reduce latency and the energy per packet by decreasing the number of hopes by 40% which is a fundamental and important factor to evaluate the system performance [15]. Pavlidis et al [34] analyzed the zero-load latency and power consumption, and demonstrated that a decrease of 62% and 58% in power consumption can be achieved with 3D-NoC when compared to a traditional 2D-NoC topology for a network size of N= 128 and N= 256 nodes, respectively, where N is the number of cores connected in the network.

However, when we talk about large-scale systems, where the number of cores can reach few thousands, the performance of such systems is still limited by the available interconnect bandwidth, and associated power budget. Infact, the power consumption is proportional to the number of cores [34], in particular, data transfer between processors and memory, between process units or between memory storage units. Thus, to achieve significant and scalable solution to the interconnect problems, real fundamental changes in system interconnect, and fabrication technologies are needed. Especially in the architecture-level, where the power consumption should be independent of the future growth of number of cores and the bandwidth requirement.

A promising approach to the above problems is the use of the integrated optics technology, which could empower an increase in the ratio between data rate and power dissipation. Photonic Integrated Circuits (PIC) use light (i.e., photons) rather than electrons to send and receive data across the chip. Recent developments in nanostructures, metamaterials, and silicon technologies have expanded the range of possible functionality of light to be used as a mean of data transfer inside the chip

### **1.3** Photonic Interconnect

Integrated photonic technology is an attractive interconnect solution that can be used to mitigate the energy and bandwidth bottlenecks that are arising in SoCs systems. Photonic interconnects can enable improved bandwidth density by leveraging wavelength-division multiplexing (WDM) to transmit concurrently multiple parallel streams of data via a single waveguide [35] with very high data rates reaching 25Gbps and 40Gbps per single channel (i.e., wavelength) [36,37]. As a result, photonics can alleviate the problems facing interconnect subsystems that are reaching limits in wire and input/output (I/O) pin density.

When using photonics in NoC architectures, the key to saving power comes from the fact that once a photonic path is established, the optical data is transmitted in an end-to-end fashion without the need for buffering, repeating, or regenerating. This is different from electronic NoCs, where messages are buffered, regenerated and then transmitted on the inter-router links several times en route to their destination. In addition, photonic routers do not need to switch to every bit of the transmitted data like in electronic routers; optical routers switch on and off once per message, and their energy dissipation does not depend on the bit rate. This feature allows for the transmission of ultra-high bandwidth messages while avoiding the power cost which found in traditional electronic networks. Higher bandwidth density is attractive from deployment and integration standpoint since it enables enormous throughput within the same or smaller physical dimensions, as in the electronic domain. The combined advantages of better bandwidth density and power efficiency make photonic interconnects a serious contender as a technological replacement for electronic interconnects.

It should be mentioned here that the difficulties of electrical interconnections are not simply ones of scaling of power and bandwidth of the interconnection system. There are a plenty of other difficulties that could be dominant reasons for changing to a radical solution like photonic interconnection. This includes issues such as voltage isolation, timing accuracy, and overall ease of design. For example, an optical link may allow larger synchronous zones in systems, not only on one chip but also possibly extending to multiple chips. The limitations in the performance of electrical interconnect at high speeds are making it difficult maintain large synchronous zones in systems. The use of photonic links helps because effective signalvelocities may be higher, compared to the electronic lines (repeated and unrepeated ) where the effective signal propagation velocity is limited to a relatively small fraction of the velocity of light (e.g., 10-20%) [38].

Another example of the benefit of using photonic interconnect is that such interconnection intrinsically provides voltage isolation between different parts of thecomponents inside the chip. In fact, photo-detectorsessentially count photons, not measure classical voltage, and provide perfect voltage isolation as a result [38].

## 1.4 Photonic Networks-on-Chip: Problems and Motivation

When using photonic links, the first challenge that faced on-chip network designers is the lack of data buffering and in-flight processing for optical beams. Two main approaches were proposed to deal with this issue. The first approach is the use of Electro-Assisted PNoC (EA-PNoC) architecture. In EA-PNoC, an Electronic Control Network (ECN) is dedicated to handling the arbitration and the routing process [39] to set the switches before the data take place in End-to-End fashion. The data is transmitted in a Photonic Communication Network (PCN) made by photonic switches [39] or crossbar [40]. This approach is characterized to be power hungry since it uses an entire network for routing and arbitration purpose. In addition, the latency overhead due to the path configuration process to enable the End-To-End transmission [41–43]. On the other hand, the use of such approach provides a huge bandwidth since the whole laser power budget will be dedicated only to the data transfer.

The second approach is the use of Wavelength-Routed PNoC (WR-PNoC) architectures [44–48]. WR-PNoCs use individual wavelengths which can be statically or dynamically allocated to source-destination pairs using combinations of modulators, filters, and waveguides. They also use wavelength selectivity to route data through the network, in contrast to circuit-switched networks (i.e., EA-PNoC) which utilize wavelength selectivity for bandwidth aggregation. Such networks are characterized by a low latency since there is no path configuration before the transmission. Furthermore, this kind of architectures has high photonic-layer complexity (e.g., more than a million ring resonators required for the implementation in [44]). Besides the complexity, the basic building block for these architectures is a ring resonator. Because of the effect of temperature variations on refractive index [49,50], the resonance frequency of the ring is shifted and leading to a miss-routing.

Both approaches have their pros and cons, while for the EA-PNoC scheme, which is used for bandwidth-sensitive workload, more attention should be given to the ECN by minimizing the path configuration overhead. In contrast with the WR-PNoC, where the design is more concentrated on minimizing the number of photonic devices (i.e., modulators and detectors), as well as the number of used wavelengths.

### **1.5** Thesis Objectives and Contributions

Starting from all the facts mentioned above, in this thesis, we propose a highperformance, scalable nanophotonics on-chip network for many-core systems. First, a novel energy-efficient and high-throughput many-core hybrid Silicon-Photonic Network-on-Chip architecture (PHENIC), is proposed. The proposed PHENIC system has a Non-Blocking Photonic Switch (NBPS) and equipped with contentionaware path configuration algorithm. The proposed system efficiently reduces the blocking occurrence resulting in reducing the total energy and increasing the system's bandwidth. We demonstrate that the proposed system has a better performance and low energy dissipation compared to conventional EA-PNoCs.

Second, to further optimize PHENIC system, a Wavelength-Routed Control Network (WRCN) is proposed, where the ECN is substituted by another plane made by photonic devices rather than electronic ones (i.e., electronic router). Moreover, a Wavelength-Shifting Routing Algorithm (WSRA) is proposed to handle the different routing and arbitration processes. The new proposed WRCP come as a compromise between the EA-PNoC and WR-PNoC architectures, where we can aggregate a considerable bandwidth (i.e., EA-PNoC) with low power and latency overhead (i.e., WR-PNoC).

The main contributions of this research are as follows:

• A new Non-Blocking Photonic Switch (NBPS) capable of handling all acknowledgment signals required for the path setup process (i.e., ACK and Tear-down). Thus, we adopt a new hybrid switching policy in the PCN: Spatial switching for the data stream transfer which is mostly used in conventional hybrid-PNoC designs. This is done by manipulating the state of the broadband switching elements. The second switching used is a Wavelength Selective Switching for the acknowledgment and Tear-down signals by using passive filters placed at the input and output of each port.

- A contention-aware path configuration algorithm [42,43] that aims to decouple the ECN from the PCN in a manner that they work independently of each other. The proposed algorithm orchestrates the different path setup packets processes; thus, significantly alleviating the contention in the ECN and its consequent energy overhead and further enhancing the bandwidth, contrary to the already proposed hybrid-PNoC architectures.

- A Wavelength-Routed Control Network (WRCN), which aim to reduce the path configuration delay, as well as the energy. The proposed architecture is augmented with Wavelength-Shifting Routing Algorithm (WSRA), which manages the different routing and arbitration processes.

- A detailed performance evaluation where we highlight the efficiency of the proposed system and the performance gain when compared to well known previously proposed EA-PNoC systems [51]. Moreover, an analytically model is proposed, where we highlight the merits of the proposed WSRA, in terms of path configuration delay and energy efficiency.

### **1.6** Thesis Outline

The rest of the thesis is organized as follows:

- In Chapter 2, we first overview the photonic on-chip interconnect main components, and we highlight the different routing schemes.

- Chapter 3 presents some of the important related works that dealt with EA-PNoC, WR-PNoC, and other architectures.

- Chapter 4 introduces the proposed non-blocking electro-optic router with its two components. The non-blocking photonic switch and the electronic controller.

- In Chapter 5, the proposed photonic architecture and the contention aware routing algorithm are discussed. A detailed performance evaluation is given at the end of this chapter.

- We dedicate Chapter 6 to introduce the proposed WRCN and the corresponding routing algorithm (i.e., WSRA). A design space exploration is performed where we compare the proposed scheme with conventional ones.

- Finally in Chapter 7, we end this thesis with the conclusion. We also discuss how this work can be optimized further.

## Chapter 2

# Background: Photonic Networks-on-Chip

In this chapter, we introduce the photonic on-chip interconnect paradigm, and we explain its principal components and the different steps that the data need to go through. We also highlight the two main approaches of routing photonic data, which are the EA-PNoC and WR-PNoC approaches. Examples from the literature are shown and we discuss the pros and cons of each approach.

### 2.1 Photonic Communication

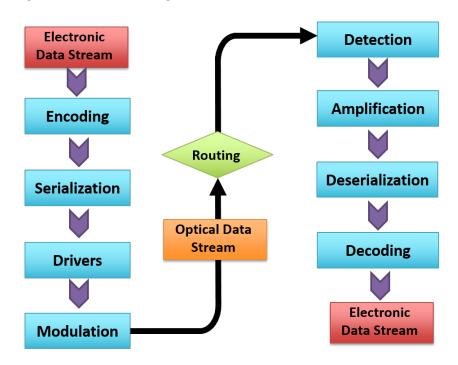

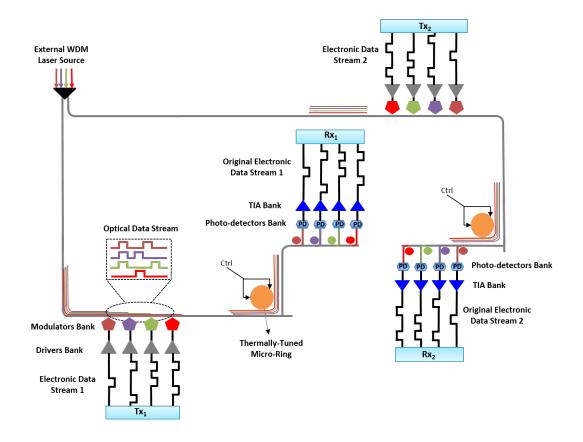

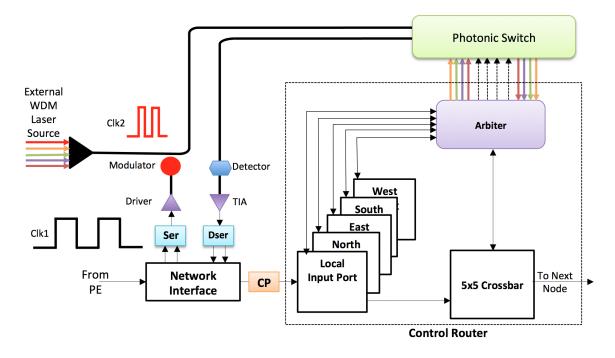

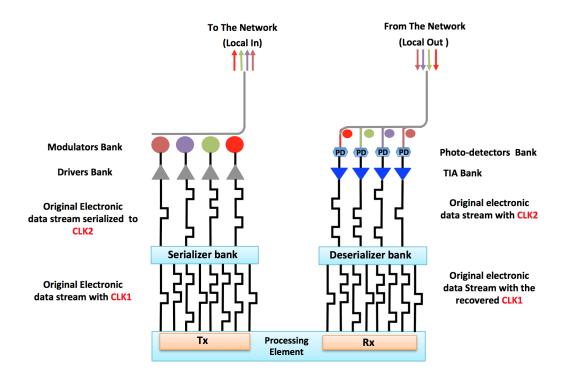

Figure 2.1 shows a functional diagram of an optical communication. The original electronic data stream is first encoded for signal conditioning. The second step is to increase the data rate (if needed) through a serialization step. The serialization step aims to reduce the number of wires required at the output by combining multiple incoming data streams (i.e., wires). The aggregate data rate remains constant before and after the serializer. Third, a driver circuit is required for each transmission wire to condition further each signal with the appropriate peak-to-peak voltage levels and to supply an adequate amount of current to drive the optical modulator. Finally, the modulator translates the electrical signal into an optical signal so that it can propagate on the photonic interconnection network. Once the original data stream is converted to the optical domain, and according to the routing process, the data

travels along the allocated waveguides until it reaches the receiver side.

Figure 2.1: Functional diagram of an optical communication.

In the receiver side, a dedicated photodetector intercepts the incoming light beam. The photodetector converts a photon stream back into an electrical current. After the detection, the resulting current needs to go through an amplification step using a Trans-Impedance Amplifier (TIA), which aims to convert the output of the photodetectors from current-based to a voltage-based signal. The next step is the deserialization step, which converts back the data rate into the original data rate (i.e., before serialization). Lastly, the decoding step is performed where the original data signal is recovered.

#### 2.1.1 Photonic NoC Building Blocks

In this section, the main photonic building blocks needed for the generation and the detection of an optical data inside a PNoC (Photonic Network-on-Chip), are introduced.

#### 2.1.1.1 Laser

Lasers emit light through a process of optical amplification based on the stimulated emission of photons. Most lasers consist of a gain medium, a pump, and a mechanism for optical feedback [52]. For photonic interconnection networks, the key laser parameters are wavelength of operation, maximum output power, power efficiency, stability, footprint, CMOS compatibility, and cost. Using off-chip laser and coupled with broadband quantum dot semiconductor optical amplifiers, many wavelength channels can be produced, with low relative intensity noise, that may be modulated, transmitted, and received. This approach alleviates packaging complexity of the silicon chip while simultaneously minimizing the overall cost and power consumption. One of the promising solutions for the off-chip laser is to use Vertical-Cavity Surface Emitting Laser (VCSEL) [53]. Such devices can be flip-chipped directly on top of the grating coupler with a strict optical alignment needed for integration.

#### 2.1.1.2 Coupler

Couplers allow on-chip components to interface physically with off-chip ones. The challenge in couplers is that the cross-section of the waveguide (on chip) is x1000 smaller than the one of the fiber (off-chip) [54]. This mismatch in the cross-section between off-chip and on-chip domains arises many problems including insertion loss, integration density, bandwidth density, crosstalk, reflectivity, and scalability. Another major challenge for each coupling technology, critical for its commercial viability, is its packaging [54].

### 2.1.1.3 Waveguide

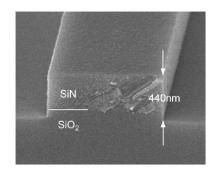

The waveguide is the basic building block in the photonic link. It is used to carry high-speed optical data stream from one point to another. In most silicon photonic applications, the high index contrast between the silicon waveguides and the silicon dioxide cladding surrounding them results in an extremely small optical mode size for single-mode operation. This condition enables very dense integration of silicon photonic devices. For example, Crystalline silicon photonic waveguides are capable of transporting wavelength-parallel optical data with tera bits-per-second data rates across the entire chip [54, 55]. In addition, as the photonic link might have irregular trajectory, waveguides can be bended [54, 56] or used to perform a crossing if needed [54, 57]. Figure 2.2 shows a cross section of a silicon waveguide.

Figure 2.2: Cross-section of a waveguide [58].

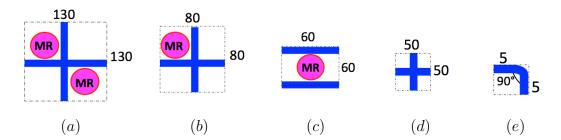

#### 2.1.1.4 Micro-Ring Resonator

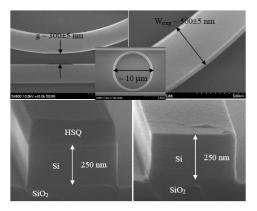

Microring Resonators (MRs) are widely used to achieve high-performance operations, switching, detection and modulation. MRRs having a high refractive index contrast are used in dense integration due to their small size. When used as dynamic components, MRs might be used as microring modulators to modulate a specific wavelength according to its Free Spectral Range (FSR). An extremely small ring will have a large FSR and allow the filtering of a single wavelength channel [54]. In addition to the wavelength selectivity, MRRs can act as broadband switches used to switch many wavelengths at the time. This technique is used for the bandwidth aggregation when multiple wavelengths are needed to deliver the required bandwidth. Such technique is used mainly in EA-PNoC, where the MRRs are tuned electronically through an integrated heater. Figure 2.3 shows scanning electron micrographs of one fabricated microring resonator with waveguide width equal to 500 nm and waveguide cross-sections at two cleaved facets.

Figure 2.3: Scanning electron micrographs of a fabricated microring resonator and waveguide cross-section at two cleaved facets [59].

#### 2.1.1.5 Modulator

The electro-optic modulator [54, 60] is a critical device that enables high-speed conversion from an electrical signal to an optical signal. By using an array of modulators, multiple wavelengths can be obtained (i.e., multiplexing). The resonant wavelength (the wavelength on which each modulator is tuned) is determined by the round-trip phase of the used micro-ring resonator. Integrated silicon modulator can operate at very high frequency reaching 25GHz [36] or even 40 GHz [37].

Figure.2.4 [61] shows a modulator with its embedded heater needed to tune to a specific wavelength.

Figure 2.4: Micro-ring modulator. (a) Cross-section of the designed modulator with a local heater and (b) Top-view SEM image of the fully fabricated microring modulator. The ring radius is 5 m [61].

#### 2.1.1.6 Photodetector

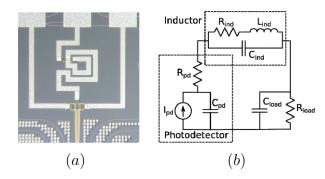

Photodetectors are the end point of a photonic link. By absorbing the incoming photons, it translates the optical data stream into an electronic one. In case where the multiplexing is used at the start point of the photonic link (i.e., array of modulators producing multiple wavelengths), an array of photodetector is needed to isolate each wavelength. In order to achieve this, a passive (selective) MR is located in front of each photodetector to intercept the required wavelength. Germanium is used as the absorbing material for photodetection, with a resulting bandwidth reaching 40GHZ [62] and 60 GHZ [63]. Figure 2.5 shows a circuit model of a germanium photodetector.

Figure 2.5: Circuit model of germanium detector with inductive gain peak.(a) Optical micrograph of the gain peaked photodetector using the 360 pH inductor. The inductor is approximately 100  $\mu$ m x 100  $\mu$ m in size [63] and (b) Inductor used to peak the frequency response of the photodetector [63].

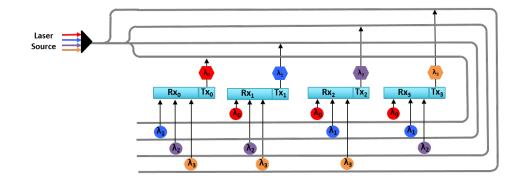

## 2.2 Routing Schemes in PNoCs

In this section, the two main routing schemes in PNoCs are described. Circuit switching used in EA-PNoCs and wavelength-selective used in WR-PNoC are the two main routing and arbitration schemes used in most PNoC architectures. Some other schemes are also used, such as Time- Division-Multiplexing [64, 65].

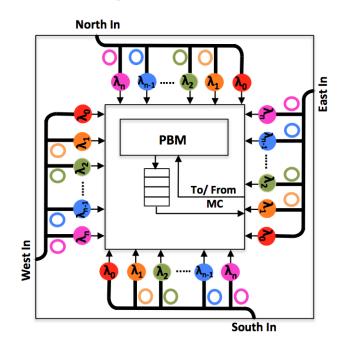

Figure 2.6: Anatomy of EA-PNoC architecture. The two communications are using the same set of wavelengths in a circuit switching scheme.

## 2.2.1 Circuit Switching

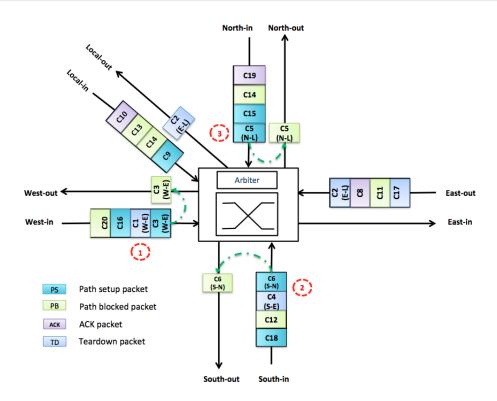

An important aspect of EA-PNoC architecture is that once a path is set, no additional processing is required to ensure a packet reaches its intended destination. This propriety comes with the cost of additional power and latency overheads. In EA-PNoC (Electro-assisted PNoC) the source node first issues a configuration packet via a copper-based electrical link to the destination node. The configuration packet is routed via the ECN (Electric Control Network) reserving the photonic switches along the path for the photonic message which will follow it in the PCN (Photonic Communication Network). It includes a source and destination addresses information and other additional control information if needed. When the destination node receives the configuration packet, it will acknowledge via an ACK packet that the path is ready for the transmission. When the ACK packet is received and processed, the source node starts the transmission of the optical data stream via the previously reserved photonic switch. When the transmission is done, the reserved path would be released by a release packet. The circuit-switched nature of these EA-PNoCs directly affects the performance and power characteristics of on-chip communication.

Figure 2.6 shows two communications between two different pairs of source and destination. We can see that both communications are using the same set of wavelengths, which provides an enormous bandwidth through WDM. In contrast with the wavelength-routed architectures where WDM is used for routing purpose, in EA-PNoC the available wavelengths (i.e., laser power budget) are completely dedicated to the data transmission, which provides a huge bandwidth needed for bandwidthintensive applications.

## 2.2.2 Wavelength-Routed

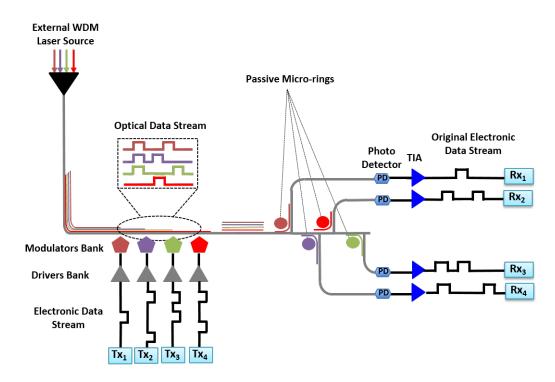

Wavelength-routed architectures use individual wavelengths allocated to a sourcedestination pairs using combinations of modulators, filters, waveguides and photodetectors. Wavelength-routed networks use wavelength-selective routing to route data between source and destination and select the appropriate wavelength through filters to be delivered to the required source, in contrast to circuit-switched where all available wavelengths can be dedicated to one communication. These architectures exhibit lower latency than electro-assisted architectures since they do not require a path configuration. On the other hand, such scheme is characterized by an excessive use of photonic devices, which increases proportionally with the number of nodes.

Figure 2.7 shows the anatomy of a wavelength routed link. Any pair of source/destination uses a unique wavelength<sup>1</sup>. The main challenge in this kind of architecture is how to use the minimum set of photonic devices/wavelengths to ensure a contention free network. In the following subsections, we show how a WR-PNoC can be built using photonic components.

Figure 2.7: Anatomy of WR-PNoC architecture. The four communications are using a different set of wavelengths.

$<sup>^{1}</sup>$ Most of the proposed architectures in the literature follow this approach to minimize the number or required photonic devices.

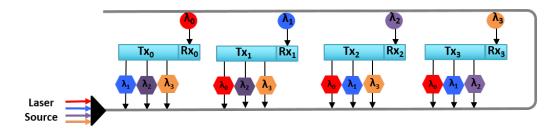

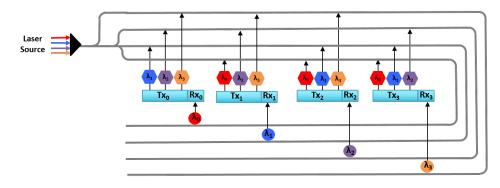

#### 2.2.2.1 Source-based Routing

The source-based routing is a configuration where each node reads from a single wavelength channel that has been assigned to it. Any other node can write to this channel. Figure 2.8 shows an implementation example with microring modulators, ring filters, and detectors. The layout uses  $N \times N$  rings and N wavelength channels, where N is the number of nodes. To prevent network collision, multiple access points must be disallowed from concurrently writing to a common destination. This could be accomplished with a separate arbitration network, such as a token arbitration ring [44].

Figure 2.8: Example of a source-based routing with four nodes. Each node receives data on a dedicated wavelength channel and transmits on all other wavelength channels.

#### 2.2.2.2 Destination-based Routing

Figure 2.9 shows the implementation of source-based routing for four nodes. In this configuration, a node modulates a single wavelength channel, and its intended destination selectively reads it. Like the source-based routing implementation, this method uses  $N \times N$  rings and N wavelength channels.

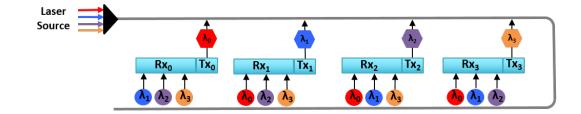

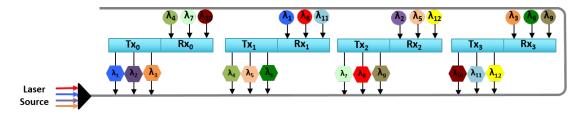

#### 2.2.2.3 Multiple Write Single Read

Another way of connecting nodes together is using a multi-write single-read (MWSR) interconnection. This kind of connection between nodes, generally involves a serpentine-like waveguide that passes through all nodes and covers the entire chip. MWSR connection can be seen in Fig. 2.10, where for nodes (each node is represented with its transmitter part (Tx) and receiver part (Rx)). Each receiver node has

Figure 2.9: Example of a destination-based routing with four nodes. Each node receives data on a dedicated wavelength channel and transmits on all other wavelength channels.

Figure 2.10: A Multi-Write Single-Read connection between four nodes.

its dedicated waveguide, where the receiver part is tuned to the (N-1) wavelength modulated by the other nodes, Where N is the number of nodes in the network. This configuration, like the source-based and destination-based schemes, requires an arbitration network to tune required modulators in each transmitter part of the node. Assuming only one wavelength for the transmission, as shown in Fig. 2.10, this configuration requires N waveguides in addition to (N-1) modulators and one photodetector at each node.

#### 2.2.2.4 Single Write Multiple Read

Figure 2.11 shows an alternative to the MWSR, which is the Single Write Multiple Read (SWMR)connection. This configuration also requires one waveguide for each node. Each node has one modulator and (N-1) photodetectors. Rings placed in front of each photo-detectors are turned ON or OFF by a separate control network.

Figure 2.11: A Single-Read Multi-Write connection between four nodes.

#### 2.2.2.5 Fully Connected Crossbar

A disadvantage of the previous wavelength-routed schemes is that they require an additional arbitration mechanism, either local or global. To avoid having to arbitrate between the nodes, a fully connected wavelength crossbar can ensure a contention free communication. As shown in Fig. 2.12, each source modulates data on a different wavelength channel depending on the destination, and each destination receives on a different wavelength depending on the source. This implementation requires  $N \times (N-1)$  modulators,  $N \times (N-1)$  photodetector (with its corresponding filter ring) and  $N \times (N-1)$  wavelength channels. As can be seen, such configuration might be not feasible for large networks, or even small ones if we consider the consequences of putting many wavelengths into a single waveguide regarding crosstalk and data correctness.

Figure 2.12: A fully connected crossbar connecting to four nodes. Each sourcedestination combination uses a dedicated wavelength.

## 2.3 Photonic NoC Metrics

In addition to the conventional metrics, such as power consumption, delay and throughput, PNoCs have other specific metrics that need to be taken into consideration when designing an efficient and reliable system. The two most important design considerations are the power budget and the data integrity.

## 2.3.1 Power Budget

The power budget here does not refer to the power consumed by the network, but it is defined as the maximum laser power that could be injected into the network without altering the photonic devices (waveguides, Modulators, etc.). In fact, the injected laser power should not exceed the nonlinear threshold of the photonic components. The nonlinear threshold is defined as the amount of power above it the photonic components start showing a nonlinear behavior. The two main nonlinear effects are the Two-Photon Absorption (TPA) [66] and the Free Carrier Absorption (CFA). These two phenomena when existing they induce a high loss [66], resonance mismatch [54] and components' alteration. The power penalty or the power loss, which is the amount of power lost between the source and the destination, will be discussed in the next chapter when evaluating the proposed switch. This loss could be caused by a crossing or by passing through or by an MRR. Consequently, the lost power will propagate inside the network causing a noise in the receiver side.

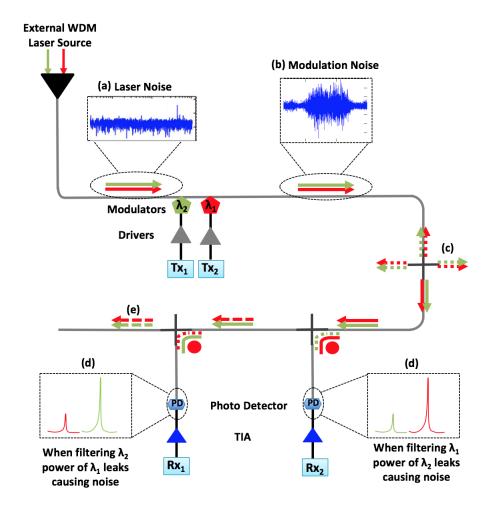

## 2.3.2 Data Integrity

The data integrity concerns the reliability of the network in terms of data correctness and how the network should be built in such a way to minimize the losses and the resulting noise. Figure. 2.13 shows an example of a resulting noise in a photonic link with two wavelengths. In addition to the noise induced by the losses, the noise can also be caused by the laser and the modulation as shown in (a) and (b), respectively. In (c), the crossing element will cause a power penalty to the signal, which lets a portion of the original signal to be spread to the other outputs of the crossing element. These small portions of power will travel across the network

Figure 2.13: Different source of noise in a photonic link. (a) Laser noise, (b) modulation noise, (c) noise due to the loss induced by a crossing element, (d) noise due to the imperfect coupling of filters, and (e) noise due to power losses traveling inside the network and coupling with other signals.

and coupled with other signals leading to additional noise, as shown in (e). Other sources of noise, is the imperfect coupling of the ring, as shown in (d). In fact, before being detected, the signal needs to be filtered. In this filtration step, some of the power will leak and will be detected with the original signal. Moreover, some other causes of noise, can be related to the thermal causes, such as Johnson [67] and Shot [68] noises.

The amount of noise in a detected signal is given by the *Signal to Noise Ratio* (SNR). From the SNR, the Bit Error Rate (BER) is calculated. In fact, due to the presence of noise in a given channel, a receiver may detect a 1 bit when the originating transmitter intended to send a 0 bit, and the BER is the rate of the faulty detected bit. Theoretically, for free error transmission the BER should be equal to zero, but a value of BER between  $10^{-10}$  and  $10^{-12}$  is also acceptable.

## 2.4 Chapter Summary

In this chapter the different steps involved in optical communication were explained. Also, the different photonic components used to build a PNoC are reviewed. We also reviewed the two main approaches for routing optical data, the electroassisted, and the wavelength routed schemes. Some photonic PNoC specific metrics such as the power budget and the data integrity were discussed. In the next chapter, some of the important works dealing with PNoCs architectures are discussed.

# Chapter 3

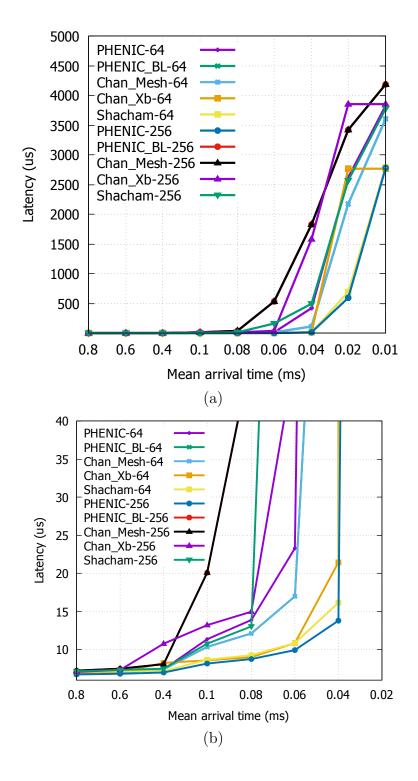

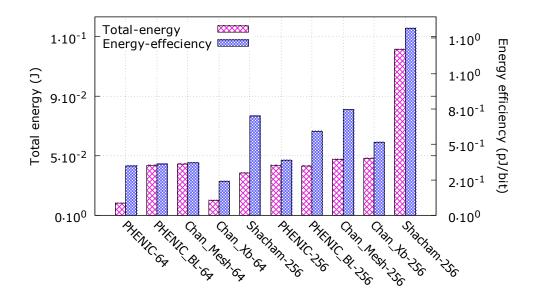

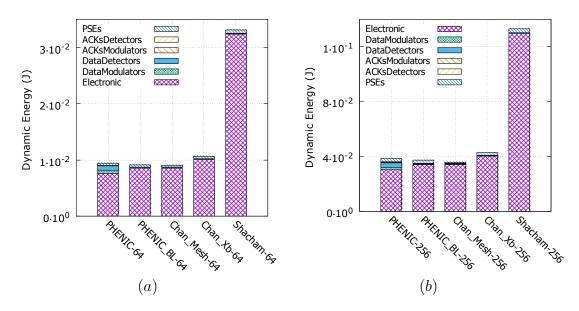

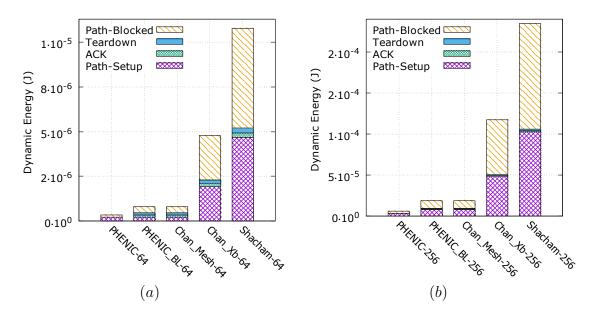

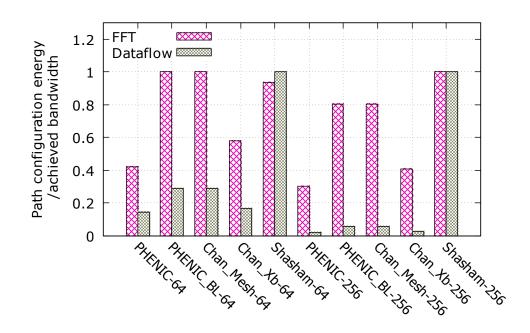

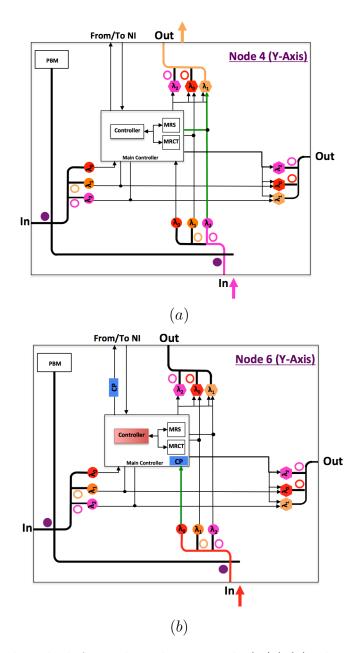

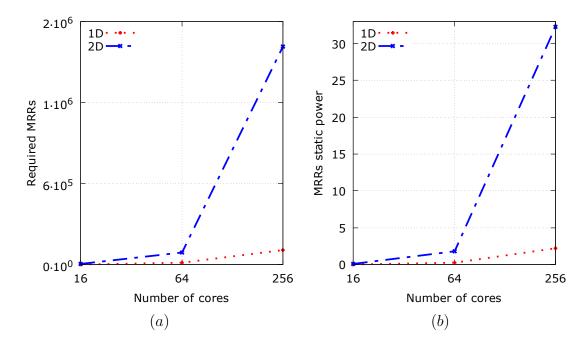

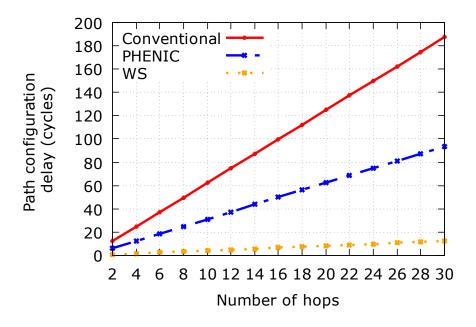

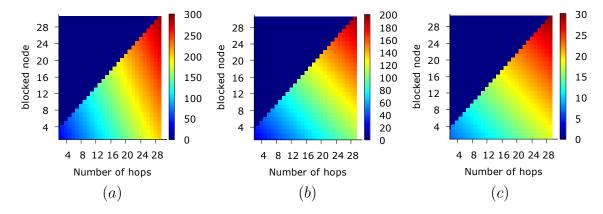

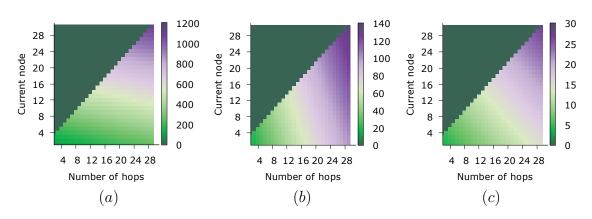

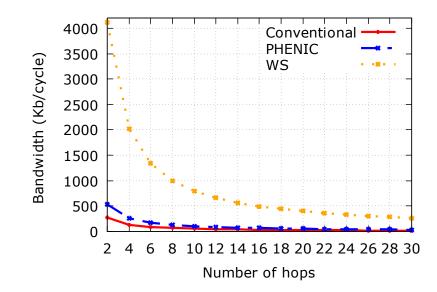

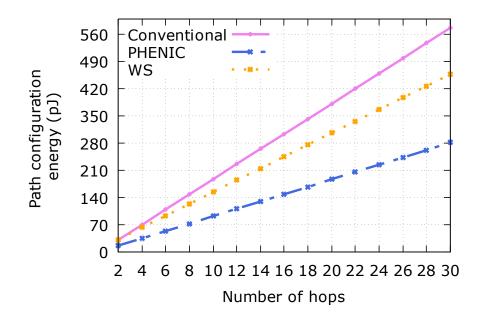

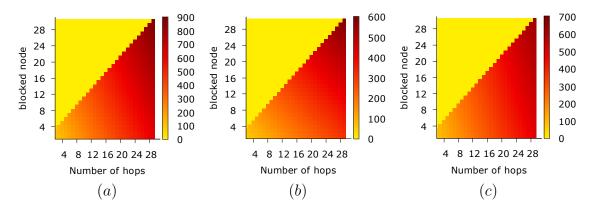

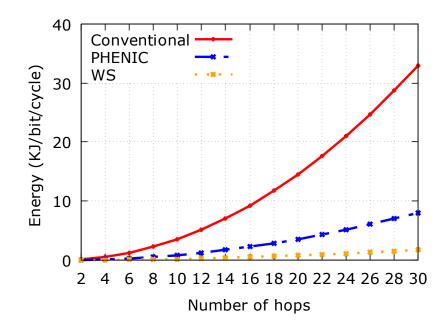

# **Related Works**